# A Design of 6t-Auto Sensing Mode of Sram for High Speed and Storage Applications

Dumpa Srinivasa Reddy<sup>(1)</sup>, Dr. VIjay Prakash Singh<sup>(2)</sup>, Dr. N Ashok Kumar<sup>(3)</sup>

(1) Research Scholar, Dept. Of ECE, Enrolment ID: SSSEC1511,

(2) Dean, HOD, Professor of ECE Dept, Sri Satya Sai University of Technology & Medical Sciences, Sehore, Bhopal (M.P.)

(3) Assistant Professor, Head Of the Department ECE ,Kasireddy Narayanreddy College of Engineering

& Research, JNTUH, Telangana.

Date of Submission: 01-06-2023

Date of Acceptance: 10-06-2023

ABSTRACT: In the digital world, Static Random Access Memory (SRAM) is one of the efficient core component for electronics design, it consumes huge amount of power and die area. In this research, the SRAM design analysis in terms of read margin, write margin and Static Noise Margin (SNM) for low power application is considered. In SRAM memory, both read and write operation affect by noise margin. So, read and write noise margins are considered as the significant challenges in designing SRAM cell. In this research, robust 6T-SRAM cell is designed to decrease the power utilization. The Auto Awake Mode is developed to control the entire 6T-SRAM cell design. The proposed 6T-SRAM- Auto Awake Mode (6T-SRAM-AAM) was implemented to reduce power utilization of understand and write down operation inside the 22 nm FinFET library. The experimental results showed the proposed 6T-SRAM-AAM design reduced power consumption of read & write operation up to 25% to 33.33% compared to existing Static RAM cells design.

**KEYWORD:** SRAM, LOW-POWER CONSUMPTION,6T- SRAM DESIGN, AUTO SENSING MODE.

# I. INTRODUCTION

Nowadays, the handheld electronic Instruments such as movable telephone, handy cam, Loptapetc.are becoming more important part of personal computing and is mainly calculated to offer a matching set of compute, message and informational apparatus in a gadget about the size of standard palm. The low down power SRAM circuits contain develop into a important component of many VLSI circuit chips [1-3].In past decades, the traditional CMOS technology has been affected by two major problems, those are less reliability and more power utilization [4]. Through a write down operation,60% of the total dynamic power require to operate bit lines in traditional SRAM cell designs [5],[6]. The Cache built on adiabatic principles is introduced based on slowly varying supply voltages [8]. This method reduces the total power dissipation, which uses several power switches and the position produce circuit in extra area overhead. To overcome the abovementioned problem, the 6T-SRAM-AAM cell is designed in this paper. The AAM is controlled by the SRAM cell design when the AAM condition was one, at the time SRAM cell perform otherwise it does not perform. The proposed 6T-SRAMAAM cell design efficiently reduced power consumption and impediment of the system balance to the 7T-SRAM cell design.

# II. CORRELATED WORK

Many researchers have suggested a numbers of the techniques for SRAM cell design. A brief evaluation of a few significant Static RAM cell designs is existing in this part. Byung-Do Yang [5] proposed a small power Static RAM using BL accuse recycle for understand writing and put in writing operations. This proposed charge recycling SRAM design was based on the hierarchical BL architecture and BL charge recycling method. The proposed method was achieved less degradation of SNM, 17% & 84% of read and write power consumption respectively achieved. other than the operation speed is inadequate to 145MHz.W. Kang et al. [9] introduced a non-volatile SRAM propose with Magnetic Tunnel Junction. They designed MAP of the MTJ device. The switching techniques provided better accumulate power, delay, and

dependability disquiet. The main limitation of the system is, it consumes more switching power. A. Makosiejet al. [10] introduced TFET-based 8T SRAM cell. The 8T SRAM cell maintains full functionality in all operation modes at 1V supply voltage with no architectural limitation linked to the half-selection problem. The cell design allowed the use of long word lines with bit interleaving. The major drawback of the Static-RAM design is, whenever the supply voltage increases, at the time substantial leakage power also increases. E. Karl et al. [11] proposed a huge presentation, voltage scaling of 162 Mb Static RAM range was urbanized in 22nanometer tri-gate bulkiness equipment. The 22 nm tri-gate technology delivered a 0.092m High-Density Cell (H-DC) bit cell and 0.108 m Low Voltage Cell (LVC)bit cell. The main limitation of the 6TStatic-RAM design is, internal sensing delay is very high. These all related works have several issues like more delay and power consumption, high critical cell design. the 6T-SRAM-AAM cell design is Here. implemented to overcome these problems and to minimize dissipation of power and delav comparasion of existing SRAM cells design.

# III. 6T-SRAM-AAM SYSTEM

In this paper, the SRAM architecture design consists of 6Ts with a symmetrical configuration that maintains the threshold voltage of the system. The SRAM plays an important role in VLSI technology due to its low-latency and large storage. A numbers of transistors employed in the SRAM circuit, which limits the reliability of the circuit. In this work, the designing based on the AAM circuit design.

The conventional 6T SRAM circuit requires three BL (like 2-BLs (BL &BL\_b) and one WL used for any read and write operations.

# 6T- AAM- SRAM Cell Design

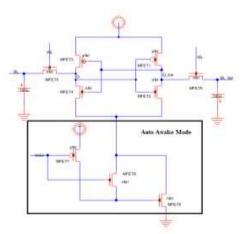

A circuit diagram of the 6T-SRAM-AAM design, which balancing several factors including area, power/leakage consumption, and speed performance.

Figure 1. 6T-SRAM-AAM circuit diagram.

The 6T-SRAM-AAM method consists of nine- MFETs. It has 2- cross-coupled inverters that show the Bi-stable latching circuitry. Two storage nodes (node1 and node2) in the 6T-AAW- SRAM, which is accessed by two-additional transistors connected to 2-BL (BL and BL\_b). These transistors are called as pass transistor and access transistor to control the storage cell in the read &write operation. Access to the cell is enabled by the WL, it controls the 2- access transistors such as MFET5 and MFET6, which are connected by BLs: BL and BL\_b. To transfer the data for both read& write operations during reading access, the BLs are actively driven low and high by the inverters in the 6TSRAM-AAM design.

# 6T- AAM- SRAM operation

The 6T SRAM is traditional choice for most on-chip memory designs. The cell design is required for balancing the several factors in terms of speed, silicon area and power consumption. The challenging issues in designing the optimum 6T SRAM cell are less cell region to obtain huge density memory, less power and low down leak current for group of cells function system. The 6T-SRAM-AAM design is based on two-different states such as read state and write state. The three different state works as follows,

# SRAM Read Operation

For a proper read operation, both the BLs such as BL and BL\_b are pre-charged to Vdd. When the WL goes high (value 1) it enables the access transistors. Some read pulses are stored in the memory after the read operation is done. If the internal node Q value is bit 1 then the internal node Q\_bar is bit 0. At the time value of the BL\_bar is bit 1 and internal node Q\_bar is bit 0. Here, the BL

and BL\_bar values are used to sense the amplifier, which act as a comparator.

#### **SRAM Write Operation**

If the content of the memory is 0 then the internal node (Q\_bar) value becomes 1 and these values are stored in Q. The WL= 1 value is required to write operation in the 6T-SRAM-AAM-. If the WL=0, it is not possible for a write operation. Here, an input operation is done by using BL and BL\_bar. The BL\_bar is connected to ground because of the internal node Q value is 0 at the time Vdd value is 1, here voltage is different so that entire system voltage is discharged.

#### 6T- SRAM Design based on AAM Operation

The AAM design has 2-PMOS and 4-NMOS. AAW design having 3T such as 1 PMOS (MFET7) and 2NMOS (MFET8, MFET9). The 6T-SRAM output is given into the MFET 8 and MFET 9, these base stations are connected to MFET7, which act as AAM. The AAM control the overall 6T-SRAM cell based on power consumption. By using AAM circuit, the static power of the SRAM design will reduce. In the AAM- SRAM cell, data will be maintained and a voltage around SRAM memory must be greater than the minimum data retention voltage. Earlier do research perform to decrease the power consumption of Static Rams design. In that design, which is employed to increase the fundamental technology of transistor size and leakage. The existing high-performance SRAM cells usean asymmetric configuration of the 6Ts It can minimize the leak by employing upper, but the usage of high transistor causesthe performance of SRAM cell by unacceptable line margin. In this research, the asymmetric SRAM cells minimize the leakage by selecting the preferred state and this also reduces the performances of transistors when cell is in the same status. The experimental results of proposed 6TSRAM-AAM cell design is briefly explained as follows.

# IV. 4. RESULT AND DISCUSSION

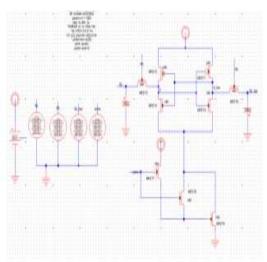

A power and delay of an SRAM cell designs are the two key design circuits in the nanometer scheme. For comparison, this paper Employed the 6 Transistors-Static RAM-AAM cell design. This paper implemented 22nm technology in FinFET library for 6T-SRAM-AAM cell design. The Schematic track diagram of the 6Transistor-SRAM –AAM is given below.

Figure 2. Schematic circuit diagram of the 6TransitorSRAM-AAM

#### Area computation

The area can be optimized by having a lesser number of cells and by replacing multiple cells with a single cell that includes both functionalities. In this paper, the transistor area is computed by transistor width and length (1Transistor = 15 (width)\*24 (length) = 360 n).

#### Power computation

The power consumption by the particular source is computed by multiplying the average current drawn from the source and voltage provided by the source.

# **Delay computation**

The Static RAM delays are termed as the time required to change Static RAM cell design one sense gate to another sense gate. The wait is computed difference of time between the 0 to 0.9 voltages.

#### Table.1. Implemented based on 22nm technology for existing methods like 7T-SRAM, 6T-SRAM, and 6TSRAM-AAM.

| Design              | Operation | Area<br>(nm) | Dynamic<br>Power (µm) | Delay (ns) |

|---------------------|-----------|--------------|-----------------------|------------|

| 7T-<br>SRAM         | Read      | 2520         | 900                   | 0.5        |

| 6T-<br>SRAM         | Read      | 2160         | 540                   | 0.1        |

| 6T-<br>SRAM-<br>AAM | Read      | 3240         | 360                   | 0.01       |

| 7T-<br>SRAM         | Write     | 2520         | 1080                  | 0.4        |

| 6T-<br>SRAM         | Write     | 2160         | 720                   | 0.2        |

| 6T-<br>SRAM-<br>AAM | Write     | 3240         | 540                   | 0.01       |

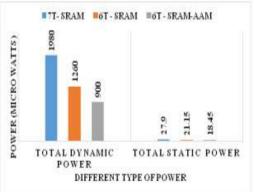

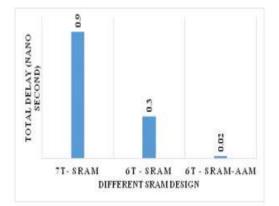

Table 1 shows the area, power and performance consumption delay of conventional 7T &6T SRAM cell design and 6T-SRAM-AAM cell design. In both methods occupied more area and consume more power. In this paper, the 6TSRAM cell is designed by using AAM, which used SRAM operation control by the AAM that improved lowpowerconsumption and delay performance compared to 7TSRAM and 6T-SRAM cell design. The comparison graph of the power and delay performances are shown in Figure 3 and 4. These results are drawn by using 20nm technology for different methodologies. According to the graph, the blue and orange color represent existing technology and the gray color represent6T-SRAM-AAM cell design. From this graph, it is clear that 6T-SRAM-AAM design consumes less power and occupied less area than the 6T-SRAM and 7TSRAM cell design.

Figure 3. Performance of delay for SRAM cell designs in 22nm technology

Tab.2. Reduced performance of total dynamic, static power and total delay for existing and 6T-SRAM-AAM design.

| Design              | Total<br>Dynamic<br>power (µW) | Total static<br>power<br>(µW) | Total<br>Delay<br>(nS) |

|---------------------|--------------------------------|-------------------------------|------------------------|

| 7T-SRAM             | 1980                           | 27.9                          | 0.9                    |

| 6T-SRAM             | 1260                           | 21.15                         | 0.3                    |

| 6T-<br>SRAM-<br>AAM | 900                            | 18.45                         | 0.02                   |

The total dynamic power, total static power and total delay performance of the existing and 6T-SRAM-AAM design shown in Table2. From the table, total dynamic power is computed based on read and write operation, if the condition WL=BL=RL=1. In Table2, it clearly shows 900 µW of total dynamic power is reduced by using 6T-SRAM-AAM design compared to existing methods like 7T-SRAM and 6TSRAM.Furthermore, if the condition WL=BL=RL=0, then the read &write operation is not possible in the SRAM circuit design. At the time the total static power is computed in SRAM cell design. The 18.45 µw of total static power minimized by the 6T-SRAM-AAM design compared to existing SRAM cell designs. As well as the total delay also reduced 0.02 ns by using 6T-SRAM-AAM design compared to existing methods. the compression graph of total dynamic/ static power performance for SRAM cell designs in 22nm technology. comparison performance of total delay for SRAM cell design in 22 nnm technology.

Figure 4. Comparison performance of total dynamic and static power for SRAM design in 22 nnm technology

Figure 5. Comparison of total delay performance for 22 nm technology

Figure 6.Performance of Read operation of the 6TSRAM-AAM design

Figure 7.Performance of Write operation of the 6TSRAM-AAM design

The Rd function of the 6TransistorStaticRAM-AAM design. The write operation of the 6T-SRAM-AAM design. The delay performance of the 6T-SRAM-AAM design is illustrated the static power performance of the 6TransitprStatic RAM-AAM design. Fig. 8 shows the conditions of BL is 0.9v, WL is 0.9v and BL\_bar is -0.9v in read operation of the 6T-SRAM-AAM design. BL is -0.9v, WL is 0.9v and BL\_bar is 0 in write function of the 6T-SRAM-AAM

design. Delay performance computed between the 12 v to 12.1v. Static power is computed by the threshold voltage (v) and current (I). Finally, the6T-SRAM-AAM design is used to calculate the static power performance of BL, WL and BL-bar.

# V. 5. CONCLUSION

The SRAM design is used for high-speed operation with less power scheme by employing small voltage swings on the bit-line margin. In this research, the 6Transitor Static RAM cell was designed in 22 nm FinFET technology based on AAM controller to minimize the power consumption of the both Rd& WR operation for real time applications.. Hence, the proposed method achieved 33.33% of dynamic power (µm) in read operation, 25% of dynamic power (µm) in existing 6T Static RAM cell.In this research, both 7Transistor SRAM and 6T SRAM cells has been designed and compare to this cell designs the proposed 6T-SRAMAAM design obtained better power consumption. In Future work, the leakage current will play significant role to minimized power consumption. By creating a layout of the transistors SRAM cell design in Xilinx or Cadence tool, it can minimize area, respectively.

# REFERENCES

- Ataei, Samira, and James E. Stine. "A 64 kB Approximate SRAM Architecture for Low-Power Video Applications." IEEE Embedded Systems Letters 10, no. 1 (2018): 10-13.

- [2]. Yadav, S., Malik, N., Gupta, A. and Rajput, S., 2013. Low power SRAM design with reduced read/write time. International Journal of Information and Computation Technology, 3(3), pp.195-200.

- [3]. Birla, S., Shukla, N.K., Mukherjee, D. and Singh, R.K., 2010, June. Leakage Current reduction in 6T single cell SRAM at 90nm technology. In Advances in Computer Engineering (ACE), 2010 International Conference on (pp. 292-294). IEEE.

- [4]. Singhal, Varun Kumar, and Balwinder Singh. "Comparative study of power reduction techniques for static random access memory." International journal of VLSI and signal processing applications 1, no. 2 (2011): 80-88.

- [5]. Yang, Byung-Do. "A low-power SRAM using bit-line chargerecycling for read and write operations." IEEE journal of solidstate circuits 45, no. 10 (2010): 2173-2183.

- [6]. Samson, Mamatha. "Stable and Low Power 6T SRAM." International Journal of Computer Applications 78, no. 2 (2013).

- [7]. Jeong, Hanwool, Juhyun Park, Tae Woo Oh, Woojin Rim, Taejoong Song, Gyuhong Kim, Hyo-Sig Won, and Seong-Ook Jung. "Bitlineprecharging and preamplifying switching pMOS for highspeed low-power SRAM." IEEE Transactions on Circuits and Systems II: Express Briefs 63, no. 11 (2016): 1059-1063.

- [8]. Nakata, Shunji. "Recent progress in Adiabatic circuits." Recent Patents on Electrical & Electronic Engineering (Formerly Recent Patents on Electrical Engineering) 2, no. 1 (2009): 40-44.

- [9]. Kang, Wang, WeifengLv, Youguang Zhang, and Weisheng Zhao. "Low store power high-speed high-density nonvolatile SRAM design with spin Hall effect-driven magnetic tunnel junctions." IEEE Transactions on Nanotechnology 16, no. 1 (2017): 148-154.

- [10]. Makosiej, A., Gupta, N., Vakul, N., Vladimirescu, A., Cotofana, S., Mahapatra, S., Amara, A. and Anghel, C., 2016. Ultra-low leakage SRAM design with sub-32 nm tunnel FETs for low standby power applications. Micro &Nano Letters, 11(12), pp.828-831.

- [11]. Karl, E., Wang, Y., Ng, Y.G., Guo, Z., Hamzaoglu, F., Meterelliyoz, M., Keane, J., Bhattacharya, U., Zhang, K., Mistry, K. and Bohr, M., 2013. A 4.6 GHz 162 Mb SRAM design in 22 nm tri-gate CMOS technology with integrated read and write assist circuitry. IEEE Journal of Solid-State Circuits, 48(1), pp.150-158.

- [12]. Ansari, Abdul Quaiyum, and Javed Akhtar Ansari. "Design of 7T sram cell for low power applications." India Conference (INDICON), 2015 Annual IEEE. IEEE, 2015.